Product Summary

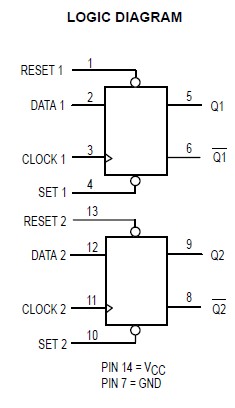

The MC74HC74AN is identical in pinout to the LS74. The device inputs are compatible with standard CMOS outputs; with pullup resistors, they are compatible with LSTTL outputs. The MC74HC74AN consists of two D flip–flops with individual Set, Reset, and Clock inputs. Information at a D–input is transferred to the corresponding Q output on the next positive going edge of the clock input. Both Q and Q outputs are available from each flip–flop. The Set and Reset inputs of the MC74HC74AN are asynchronous.

Parametrics

MC74HC74AN absolute maximum ratings: (1)DC Supply Voltage (Referenced to GND): -0.5 to + 7.0 V; (2)DC Input Voltage (Referenced to GND): -0.5 to VCC + 0.5 V; (3)DC Output Voltage (Referenced to GND): -0.5 to VCC + 0.5 V; (4)DC Input Current, per Pin: ±20 mA; (5)DC Output Current, per Pin: ±25 mA; (6)DC Supply Current, VCC and GND Pins: ±50 mA; (7)Power Dissipation in Still Air, Plastic DIP: SOIC Packag: 500 mW, TSSOP Packag: 450 mW; (8)Storage Temperature: -65 to + 150 ℃; (9)Lead Temperature, 1 mm from Case for 10 Seconds (Plastic DIP, SOIC or TSSOP Package): 260 ℃.

Features

MC74HC74AN features: (1)Output Drive Capability: 10 LSTTL Loads; (2)Outputs Directly Interface to CMOS, NMOS, and TTL; (3)Operating Voltage Range: 2.0 to 6.0 V; (4)Low Input Current: 1.0 mA; (5)High Noise Immunity Characteristic of CMOS Devices; (6)In Compliance with the Requirements Defined by JEDEC Standard No. 7A; (7)Chip Complexity: 128 FETs or 32 Equivalent Gates.

Diagrams

| Image | Part No | Mfg | Description |  |

Pricing (USD) |

Quantity | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|

MC74HC74AN |

ON Semiconductor |

Flip Flops 2-6V CMOS Dual |

Data Sheet |

Negotiable |

|

||||||||||||

|

MC74HC74ANG |

ON Semiconductor |

Flip Flops 2-6V CMOS Dual D-Type w/Set Reset |

Data Sheet |

|

|

||||||||||||

(Hong Kong)

(Hong Kong)